← Back to Projects

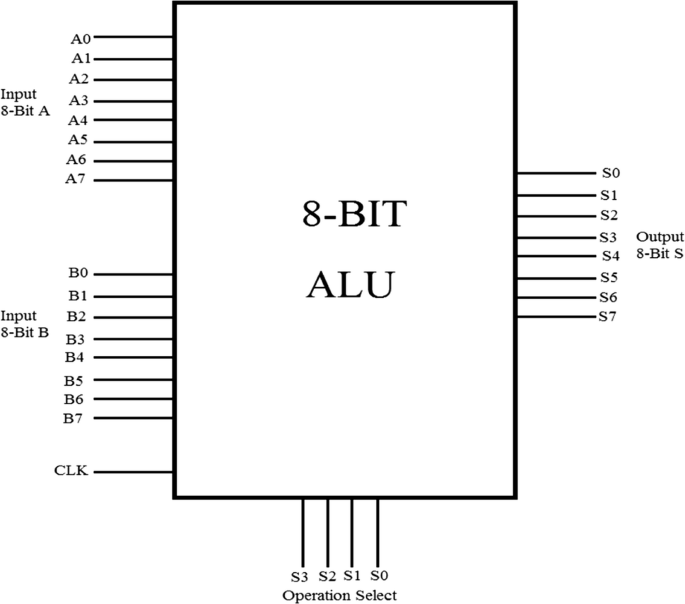

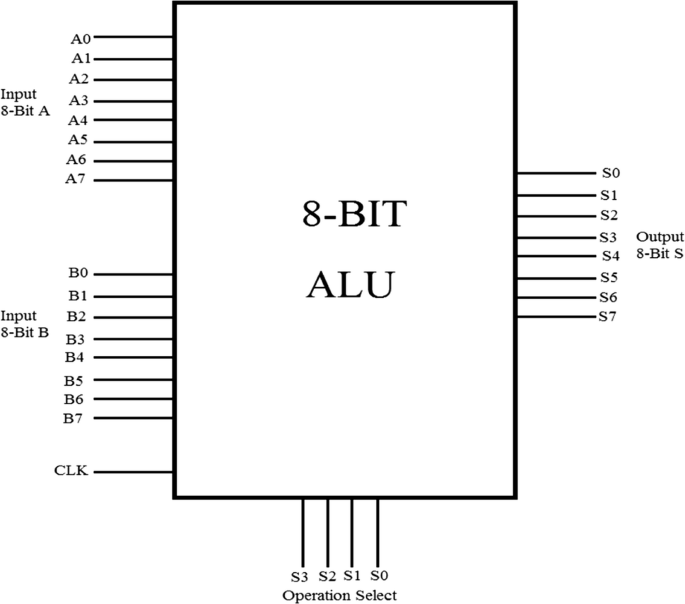

Designing and simulating a 8-bit ALU

The ALU is implemented as a combinational logic circuit, where the output is directly determined

by the instantaneous state of the inputs.

● Inputs: The module accepts two 8-bit binary operands, A and B.

● Control Mechanism: An Opcode serves as the control signal, selecting the specific

operation to be performed.

● Operation Execution: A case statement is used to map the Opcode to the

corresponding operation, which includes common functions like addition, subtraction,

AND, OR, and other bitwise operations.

● Outputs: The result is provided as an 8-bit output. Additionally, flags such as Carry (to

indicate overflow) and potentially Zero (to indicate a zero result) are generated for

arithmetic operations.

● Verification: Since no physical hardware was used, a Verilog Testbench was created to

simulate the design and process the inputs. The functionality and correctness were

verified by analyzing the resulting digital waveforms in the timing diagrams.

by the instantaneous state of the inputs.

● Inputs: The module accepts two 8-bit binary operands, A and B.

● Control Mechanism: An Opcode serves as the control signal, selecting the specific

operation to be performed.

● Operation Execution: A case statement is used to map the Opcode to the

corresponding operation, which includes common functions like addition, subtraction,

AND, OR, and other bitwise operations.

● Outputs: The result is provided as an 8-bit output. Additionally, flags such as Carry (to

indicate overflow) and potentially Zero (to indicate a zero result) are generated for

arithmetic operations.

● Verification: Since no physical hardware was used, a Verilog Testbench was created to

simulate the design and process the inputs. The functionality and correctness were

verified by analyzing the resulting digital waveforms in the timing diagrams.

The core objective of this project was to design and functionally verify an 8-bit Arithmetic Logic Unit (ALU) using behavioral Verilog HDL. As a fundamental component of a Central Processing

Unit (CPU), the ALU is responsible for executing both arithmetic and logical operations.

Source Code

Files

Select a file

Loading...

Click folders to browse. Click a file to preview its code here.